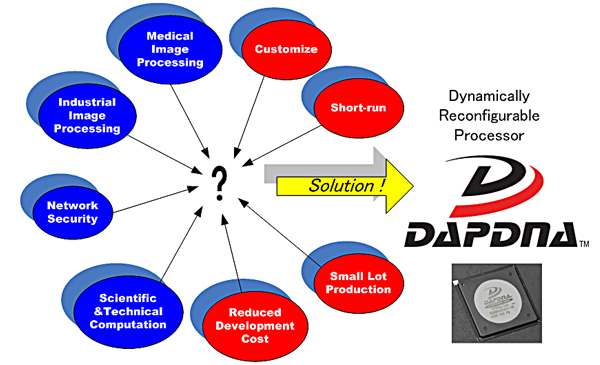

With ever growing demand for high-speed processing of large volumes of data to respond to sophisticated requirements in industrial and medical image processing, communications, network security, scientific & technical computation, and other applications and amid the reality of accelerated product development cycles involving customized but short-run and small lot production and demands for reduced development costs, the dynamically reconfigurable processor, DAPDNA, offers a powerful, cost effective solution for such processing needs.

The DAPDNA processor is capable of changing its internal hardware configuration and functionality while the system is running, adapting to changes in the environment as necessary. With multiple processing tasks performed by a single chip, it is a very cost effective alternative to the conventional approach which requires several specialized chips. DAPDNA’s architecture and platform provides the processing performance of hardware with the flexibility of software.

DAPDNA is comprised of a dynamically reconfigurable 2-dimensional distributed network architecture (DNA) - a matrix of several hundred processing elements (PEs) and a 32-bit RISC digital application processor (DAP) which controls the dynamic reconfiguration of the DNA. With each processing element arranged in the DNA’s unique PE matrix executing conventional processor instructions, parallel processing at ultra high speeds is achieved by the data interaction among PEs.

Unleashing the Power of DAPDNA in Image Processing

Recent years have seen the advent of high speed computing and high level digital processing that have made possible image scanning and data interpretation by machine systems. There is a lot of research related to image processing with equipment incorporating cameras and PCs. Here, the flexibility to adapt the processing to respond to changing conditions and environment has been a challenge in the development of such equipment. The ideal solution involves software processing but the enormous volume of data entailed in image processing requires high-speed processors.

Dynamically reconfigurable processors (DRP) were developed to provide high speed processing capability but with lower power consumption (i.e. low operating frequency). It is adaptable to a wide range of applications and image processing is said to be among the most promising.

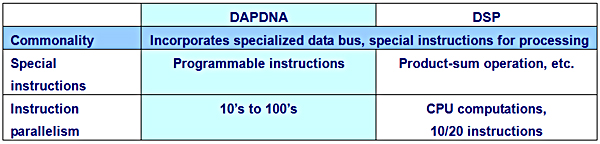

In image processing, although there are applications particularly suited to FPGA (field programmable gate array) type hardware-based processing or DSP (digital signal processing) type software-based processing, DAPDNA provides throughput equivalent or better than FPGA but with a similar degree of programmability as DSP processors. The DAPDNA processor also features low power consumption, fast and large capacity DRAM I/F, and a high speed I/O which enable system construction with fewer parts.

In addition to offering superior flexibility and extendibility, DAPDNA processors also provide a great degree of redundancy and parallelism. Flexibility is achieved by the DAPDNA processor’s ability to dynamically reconfigure hardware during system operation, an attribute which empowers multifunction printers and precision inspection equipment that incorporate image processing. DAPDNA is also envisioned as an ideal processor in applications such as robotics which involve complex and diverse motion control.

DAPDNA and FPGA Comparison

DAPDNA and DSP Comparison

NEW!DAPDNA-IM2

For faster and more cost effective image processing

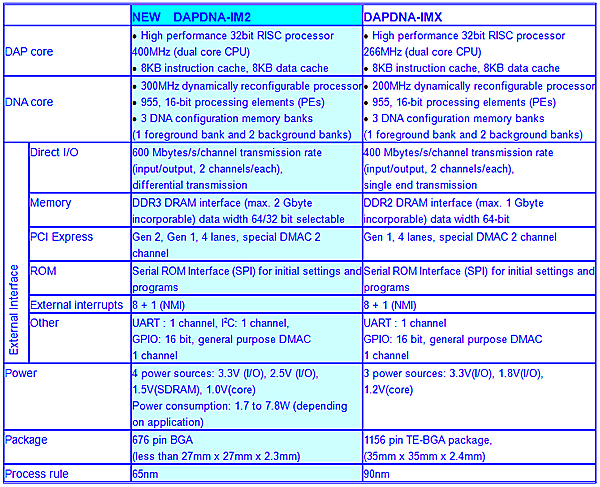

With processing speeds one and a half to two times that of the current DAPDNA-IMX processor, the new DAPDNA-IM2 processor builds on the high reputation garnered by its predecessor as a flexible and powerful support tool for image processing. The DAPDNA-IM2 boasts greatly increased processing speeds, enhanced functionality and lower costs as well as a substantially reduced footprint. Software compatibility with the DAPDNA-IMX is retained which ensures effective use of existing design assets.

Features:

Significant increase in clock frequency

Compatibility with mainstream PCI Express and DDR3 SRAM interfaces

Footprint size 60% of the DAPDNA-IMX

An integrated design environment and DAPDNA-IM2 evaluation board will also be commercially released at the same time.

New DAPDNA-IM2 and Existing DAPDNA-IMX Processors

- Differences and Commonalities -